Это копия, сохраненная 15 января 2020 года.

Скачать тред: только с превью, с превью и прикрепленными файлами.

Второй вариант может долго скачиваться. Файлы будут только в живых или недавно утонувших тредах. Подробнее

Если вам полезен архив М.Двача, пожертвуйте на оплату сервера.

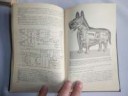

450 Кб, 800x505

450 Кб, 800x505>на тактовой частоте 1 ГГц

Ты совсем охуевший? Такие частоты разве что последние поколения тянут. Отладка с такой ПЛИСиной стоит не менее нескольких тысяч долларов.

>Такие частоты разве что последние поколения тянут. Отладка с такой ПЛИСиной стоит не менее нескольких тысяч долларов.

В курсе. Я же говорю, что не собираюсь ничего отлаживать/прошивать. Это проект кодера для системы связи со скоростью передачи данных 1 Гбит/с. Там одно только оконечное оборудование не менее 10к долларов стоит. Лучше расскажи про

>Какие основные характеристики платы нужно учитывать при её выборе?

Буду признателен.

Это говно, тактовая отсутствует как класс, памяти нет, самопрошивки тоже. Смысл только чтобы эмулировать процессор и быструю логику? Лучше взять малинку, дешеве и перефирии больше.

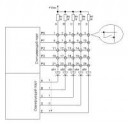

56 Кб, 1580x700

56 Кб, 1580x700>малинку

Что это?

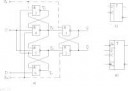

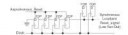

Ладно, чтобы было понятней, пикрилейтед - rtl схема кодера. Какие ксайлинковские/алдеровские платы подойдут для реализации такой байды с тактовой частотой 1 ГГц?

У пидоров сегодня в моде ПЛИС?

То есть ты хочешь, чтобы указанное тобой на пике говно, скакало с частотой гиг?

Попробуй вот эту плату

http://www.xilinx.com/products/boards-and-kits/EK-V7-VC707-G.htm

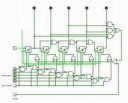

6 Кб, 220x187

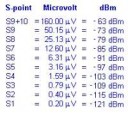

6 Кб, 220x187Как оказалось, это говно скачет на частоте гиг даже на кристалле семейства virtex 4. Пикрилейтед. А на дорогущем седьмом виртексе при тайм констрейнте 1 нс выше ~750 МГц работать не хочет.

Почему не может? У меня же всего 5 логических элементов, сгруппированных у входных/выходных пинов. Вот сильно загруженный логикой кристалл такую частоту не потянул бы, да.

Речь вообще-то шла о тактовой частоте синхросигнала. В моей схеме тактовая частота синхросигнала привязана к скорости передачи данных - 1 Гбит/с. За эту наносекунду тактового сигнала все сигналы в схеме успевают дойти от одного триггера до другого (задержка через критический путь - 0,868 нс).

Мне почему-то казалось или я где-то слышал, что Виртексы пятые можно максимум до 400МГц раскачать, более старые - соответственно до еще меньших частот.

Охуеть блять. Но что у седьмых Кинтексов сраный BUFG может работать максимум на 750МГц - это вообще пушка.

Меня тоже удивил результат, но верю на слово ксайлинковскому САПРу.

Ладно хоть этот чудом не утонул.

http://www.joelw.id.au/FPGA/CheapFPGADevelopmentBoards

Проблема в том что у нас хрен что купишь, а если учесть санкции то вообще пиздец.

С помошью SERDES переводишь входные последовательные данные в паралельные, обрабатываешь на кратно меньшей скорости, и потом преобразуешь назад.

144 Кб, 683x1024

144 Кб, 683x1024Сложна ли реализация его для плис? Нужен ли какой-то особый драйвер для пекарни/кьюбиборда?

UPD: может проще Ethernet с PPP поверх него? Ethernet PHY с разъемом на моей борде имеется.

Но ведь его заебешься реализовывать. И не понятно, как с ним работать хосту. Надо драйвер будет писать.

Можно линупс поставить.

МАТАН ТРОЛЬ уровень1024

привет, радон. суть такова: надоели мне контроллеры и стандартная логика, захотелось поизучать ПЛИС. взял ширпотребную CPLD EPM240T100C5N

в квартусе разобрался, marsohod.org весь прочитал

логику работы понимаю, в симуляторе все отладил, но во тв железе никак не выходит.

развел плату, протравил, все напаял, залил через USB-Blaster, светодиодики сразу забегали как и планировал, но вот вторая часть не заработала. попробовал отладить через JTAG с помощью In-System-Sources-and-Probes, но вообще нихуя не залилось, выдает только ошибку JTAG. контакты все прозвонил. да и вообще плата просто лежала 3 дня, пока я читал доки.

что за хуйня, анон? что я делаю не так?

пару месяцев назад я пробовал сделать демоплату типа того же марсохода и с ней произошло то же самое - 3 дня лежала и испортилась. точнее вообще тестер выдавал, что питание и земля замкнуты.

может стоит заказать плату с какого-нибудь seedstudio? в чем вообще проблема может быть?

Да. делай как анон говорит. И еще проверь на непропай. А еще проверь все земли и питания, в плис или клпд можно запитать не все банки, тогда логика будет работать, а ноги нет.

240 Кб, 1000x679

240 Кб, 1000x679Altera signal tap пробовал?

458 Кб, 660x495

458 Кб, 660x495Или может не стоит отговаривать?

Стоит отдельно отметить, что это open-source, исходники софта и железа в открытом доступе.

http://www.seeedstudio.com/depot/Bus-Pirate-v4-p-740.html - универсальный reader/writer мира мк

http://www.seeedstudio.com/depot/Open-Workbench-Logic-Sniffer-p-612.html - логический анализатор, 32 канала

Поддерживаемые протоколы

http://sigrok.org/wiki/Protocol_decoders

204 Кб, 300x400

204 Кб, 300x400Забыл добавить, что разориться на оборудование, решил для лёгкого старта знакомства с мк.

И, собственно вопрос по мк. Что лучше- брать дев.борды на каждую архитектуру, и не заморачиваться с распайкой, или покупать микрухи отдельно и колхозить заказ печатных плат у китайцев? Может дешёвые dev-kits в продаже имеются? И какие контроллеры (десятка самых популярных, к примеру) лучше брать, чтобы всё сразу, и не закупаться по сто раз?

И да, буферный теоретический минимум имеется если что, а с ардуино-мигалок начинать как-то не камильфо.

1,2 Мб, 300x162

1,2 Мб, 300x162`include <filename>

или гугли $readmemb $readmemh

Они точно работают в симуляторе, для RTL вроде тоже вроде, не пробовал

7 Кб, 200x200

7 Кб, 200x200Спасибо, анон. `include <filename> вероятно мне не подойдет, а $readmemh порпобую. Не уверен, правда, что будет работать. Помню пробовал заюзать $sformat для того, чтобы генерировать название .mif файла. Было несколько модулей с блоками памяти, каждую из которых надо было инициализировать своим файлом (file1.mif - для первого, file2.mif - для второго, ну и так далее). Дак этот ебаный квартус начал пояснять мне за несинтезируемость этого самого $sformat. Сука, как же мне печет от этих ваших HDL-языков! Нельзя что-ли было сделать что-то вроде комбинации препроцессора с большими возможностями + полностью синтезируемого языка?

>Есть более изящные языки?

Изящные? Эстет чтоли дохуя?

>Чем твой хуйлинкс лучше?

Документация пизже. И новая Вивада, по сравнению с обоссаным Квартусом, - небо и земля.

Как раз таки vhdl - говно с душой, дающее максимальное приближение к железу. Прошивка ПЛИС - это не программа, коей хотят ее видеть неосиляторы. Прошивка - это железо и для описания железа vhdl куда более пригоден.

>Прошивка ПЛИС - это не программа, коей хотят ее видеть неосиляторы. Прошивка - это железо и для описания железа vhdl куда более пригоден.

Ты тупой еблан, который про Verilog, судя по всему, лишь где-то когда-то слышал, что его синтаксис похож на Си.

Пример цифрового элемента, который естественно и удобно описывается на VHDL и не может быть естественно и удобно описан на Verilog?

В верилоге нет пакетов с функциями синуса и косинуса. Только если самому писать.

>В верилоге нет пакетов с функциями синуса и косинуса. Только если самому писать.

И это у тебя называется "VHDL более пригоден для описания железа" и, особенно, "прошивка ПЛИС - это не программа, коей хотят ее видеть неосиляторы"? Не говоря уже о том, что для генерации LUT есть матлаб.

Нет, это называется "приведи пример элемента, который естественно и удобно описывается на VHDL и не может быть естественно и удобно описан на Verilog".

Я вот фанат верилога. Считаю его более близким к железу. Программа написана на верилоге ВСЕГДА короче чем то же на ВХДЛ. А еще строгая типизация не нужна, бегин енд тоже ненужен.

Прошивка это такой процесс, когда феритовые кольца прошивали проволкой. в колечно 1, мимо - 0. Остальное демагогия.

Правильно называть: язык описания аппаратуры

Функция, которая в compile time генерирует набор коэффициентов для загрузки в блочную память, не является "цифровым элементом".

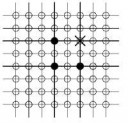

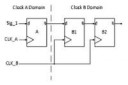

26 Кб, 1330x442

26 Кб, 1330x442Во-первых, не занудничай.

Во-вторых, прошивка - это то, что грузится в микросхему, а никак не язык описания.

>>140663

Блочная память с загруженными коэффициентами, в свою очередь, является "цифровым элементом".

>>140661

>А еще строгая типизация не нужна

Нужна, незаменимая вещь, если уметь ею пользоваться.

>Блочная память с загруженными коэффициентами, в свою очередь, является "цифровым элементом".

Но ни способ генерации этих коэффициентов, ни описание этого способа не является "цифровым элементом" или его частью. Ты можешь обосновать, почему Верилог дальше от железа, чем VHDL? Функция для расчёта коэффициентов в compile time тут точно нерелевантна.

То, что все, что ты напишешь, потом проходит через компилятор. А поскольку строгой типизации нет, компилятор может из написанного сгенерировать непойми что, вместо знакового числа сделать беззнаковое и наоборот.

Т.е. верилог как си, а вхдл - как асм. Первый конпелируется, второй - преобразуется по таблице байткодов напрямую в машинный йезык.

И тот и тот компилируется, не тупите. ВХДЛ скорее с++ или даже паскаль.

>Т.е. верилог как си, а вхдл - как асм.

Почему "т.е."? Асм это язык со слабой типизацией. Никто не помешает тебе вычислить число с плавающей точкой, потом сложить его экспоненту и мантиссу как два целых числа, а потом результат использовать как указатель. В языках с сильной типизацией за такое бьют по пальцам, но не потому что они ближе к железу, а потому что быдло до неявного преобразования типов допускать нельзя, оно не осилит даже строгого набора правил, по которым происходит неявное преобразование типов, всё поломает и будет ругать компилятор, будто бы он делает не пойми что.

Я так понял, что в твоём представлении банально "чем больше ебли, тем ближе к железу".

Асм ближе к железу, именно поэтому на нем можно сделать это: вычислить число с плавающей точкой, потом сложить его экспоненту и мантиссу как два целых числа, а потом результат использовать как указатель.

Как раз в си будет больше ебли, чтобы провернуть вышеописанное.

Ну так и чего? Ты мне доказываешь, что асм ближе к железу из-за слабой типизации, вхдл ближе из-за сильной типизации. Ты уж определись, как типизация влияет на близость к железу.

>Как раз в си будет больше ебли, чтобы провернуть вышеописанное.

В Си будет на порядок меньше ебли потому что в нём в принципе на порядок меньше ебли, а всё вышеописанное делается стандартными способами любым, кто осилил K&R.

>в твоём представлении банально "чем больше ебли, тем ближе к железу"

Я не он.

В моем представлении схема должна работать так, как ты ее описал. Поэтому, в моем представлении, язык должен давать максимум возможностей к описанию схемы. И компилятор тут лишний.

Каким образом слабая типизация лишает тебя возможностей к описанию схемы? На всякий случай напомню, что неявное преобразование типов не отменяет возможности использовать явное, и лишь позволяет в ряде случаев не писать безумные развесистые конструкции VHDL-ного типа, когда преобразование, предлагаемое по умолчанию, тебя устраивает. Это не более чем мелкое удобство, сокращающее количество набираемого текста и не влияющее на результат при условии, что ты знаком с правилами неявного преобразования.

>В Си будет на порядок меньше ебли

В асме это джве-три команды например.

А в си - ебля с преобразованиями типов.

Как в верилоге задать состояния конечного автомата? В vhdl пилишь новый тип с перечислением всех состояний, потом пилишь case. А в верилоге как?

>А в си - ебля с преобразованиями типов.

Не ссы, поставить (int) - это только в первый раз страшно.

>>140714

>В vhdl пилишь новый тип с перечислением всех состояний, потом пилишь case. А в верилоге как?

[code]

parameter [1:0] state0=0, state1=1, state2=2;

reg [1:0] state;

(...)

case(state)

state0:

(...)

state = state1;

(...)

[/code]

Ближе к железу, кстати.

Считать/записать значения в альтеровские плис можно с помощью In-System Source and Probes. Вместо gui можно написать скрипт на TCL.

Развесистые конструкции в VHDL появляются из-за неправильного использования типизации. Развитая система типов в VHDL позволяет проще реализовывать сложные конструкции.

C Xilinx не работал, поэтому не знаю.

Вроде бы оно. Спасибо.

Надеюсь господа полицейские радача не решат, что я попиариться пришел.

Есть один проект тематики /ra/ https://2ch.hk/prj/res/1.html (

Приглашаю всех к обсуждению. Есть часть, связанная с ПЛИСами. Вдруг кто-нибудь захочет присоединиться.

Я покупал у китайца вот такую плату http://www.ebay.com/itm/ALTERA-FPGA-NIOS-CYCLONE-IV-EP4CE15-USB-BLASTER-Power-Adapter-Many-Gift-E082-/261058354313?ssPageName=ADME:X:eRTM:US:1123

Относительно дешево, на борту много чего есть. Из инструкций нужна все равно только принципиальная схема.

Да ты охуел! Студенческая цена всей платы ниже чем цена камня установленного на ней.

http://www.digikey.com/product-search/en?x=11&y=9&lang=en&site=us&keywords=EP4CE115F29C7

ну и нахер нужны эти ваши плис? за такие то деньги.

у нас на заводе 10+ работает полусоветская релейная промавтоматика, управляемая PIC'ами, и всех все устраивает, работает надежно, новое никому не нужно

вы представляете сколько PIC'ов можно купить за эти деньги? то-то же. ПЛИС - бестолковый проеб бабла, ящитаю.

Ну вот и работай дальше на своем заводе.

ПЛИС - таки годнота, но задачи у него специфические. Пики - это МК, они дешевы, но имеют низкие частоты, и высокие задержки, притом не гарантированные.

Ну а где требуется риалтайм или огромные потоки данных - требуется чистая логика, с минимальными и гарантированными задержками. Тут и приходят на помощь плисины - чем сочинять 100500 плат на к155, лучше купить одну плисину и закодить схему в одном корпусе.

Так что дорого - это от раздолбайства, на самом деле плисины очень дешевы, всего то сотня баксов, и получаешь аналог кучи плат, каждая из которых стоила бы не меньше.

Ну а если плисину ставят туда, где хватит МК - это раздолбайство в чистом виде, там да - дорого.

Вот всякие заводчане и лезут со своими куллсторями, как плисина управляет двумя реле по сигналу с кнопки, лол.

> релейная промавтоматика, управляемая PIC'ами

Для кого сука плк придумали, не, не хотим, хотим жрать говно.

Ну естественно, а ещё они стандартизированны и их программу есть шанс поправить.

Ишь, USB на борту. DE1 попроще будет, там USB только для программирования. Пока запустил прием и передачу через COM порт, запустил VGA и сделал на четверть теннис на одного игрока (мячик-стенки-ракетка). Надо в него проигрыш вставить.

>ну и нахер нужны эти ваши плис? за такие то деньги

>Фор фан же

Ну разве что.

Не знаю, реализовали ли снес на ардуине лол, но уж на ежевике точно есть.

Ты не понимаешь сути плис, мудило. ПЛИС это не какой-то хитровыебанный микропроцессор, это в прямом смысле слова переконфигурируемое железо, оно обеспечивает недостижимую для программных решений скорость вычислений, естественно если пытаться закручивать винты молотком ты никаких преимуществ не увидишь, у них своя ниша.

А ты про это. Обработку 100 ГБит эзернета ты можешь на ардуине сделать? А на ПЛИС можно.

Ты умственно отсталый что ли? Как ты думаешь в топ-энд сетевом оборудовании данные обрабатываются?

Ты меня затролел своей тупостью.

Ну уж явно не плисами, лол, нахуй эти игрушки когда производители "топ-энд" оборудования могут сразу все в железе сделать.

Ага, особенно когда тираж конечных изделий пара тысяч штук. Сразу все в железе делают. Заказывают две тысячи микросхем на тайваньских фабриках.

>Cделать сразу в железе

>Устройство, которое неизвестно как будет работать в реальных условиях

>И подготовка к производству которого стоит овердохуя зеленых президентов

Da ti ohuel! Алсо ПЛИСы используют в оборудовании ОПСОСЫ, т. к. внезапно может потребоваться модернизация под новые стандарты сетей

Так и запишем - ПЛИСы для нищебродов и микро-контор. Непонятно правда причем тут

>в топ-энд сетевом оборудовании

>Алсо ПЛИСы используют в оборудовании ОПСОСЫ, т. к. внезапно может потребоваться модернизация под новые стандарты сетей

Так и представил себе опсоса с собственным оборудованием, ололо. Контроллер "МТС-3000" на базе альтерры с прошивкой от Васяна, сегодня 3ж, завтра 4ж, только Васян проспится.

Ты вообще представляешь себе что ты несешь? Да эти пидоры-производители оборудования удавятся скорее чем софтом новый стандарт сделают. Им это меньше всего нужно. Хочешь лте тдд - бери железку. Хочешь лте фдд - прости, вот тебе другая железка, ту можешь выкинуть.

> ПЛИСы для нищебродов и микро-контор

Ох лол, погугли-ка цены на IP-ядра и топовые плисы, петушок. Слишком толсто ты тралишь

Во-первых, оборудование на плисах делают не сами ОПСОСЫ. Во-вторых, продавать можно не железку, а дизайн, а цену задирай как хочешь, ведь твое оборудование уже купили. В-третьих, попробуй потоньше.

>Во-вторых, продавать можно не железку, а дизайн, а цену задирай как хочешь, ведь твое оборудование уже купили.

Ты, наверное, хотел сказать "лицензии", а не дизайн, ну да хуй с тобой. Пруф хоть один будет апгрейда железа на "новые стандарты сетей" или сольешься?

Хотя ладно, держи и на апгрейды.

http://www.cisco.com/c/en/us/td/docs/routers/7200/configuration/feature_guides/fpd.html

Как ты в тред пролазишь, толстячок?

Спасибо.

и в нем ссылку на ценник каких-то французов с минимальной партией в 25 кристаллов: http://cmp.imag.fr/products/ic/?p=prices

Для тех, кому лень учить английский: за квадратный миллиметр кристалла от 650 евро (350 нм технология) до 15000 (28 нм). Не сверхъестественно, но и недешево.

Так что для серий в сотни-тысячи изделий ПЛИС выйдет дешевле. Я уж не говорю про стоимость исправления ошибок дизайна - в случае ASIC вся партия идет на выброс.

Одного дня - нет, недели точно хватит.

Да, без проблем. Буферы не синхронный, если не укажешь явно. Погугли, например, как подключить к плис кварц, думаю будет ясно.

Двач, задавай вопросы, скучно же.

У меня 2014.2. Кстати, а зачем ты Виваду ставишь? Собираешься сразу с седьмой серией работать?

Студентота-кун репортинг ин.

В универе успел немного познакомиться с плисами и vhdl, только вот это длилось только один семестр ебаный бакалавриат.

В любом случае, хочу продолжить освоение, но уже сам, посему реквестирую книг про systemverilog.

Одно дело, конечно, уметь кодить и понимать работу плисов, но было бы еще круто узнать, как найти в рашке работу связанную с ними, да послушать успешных анонов. Навскидку в голову приходят небольшие частные конторы, занимающиеся сетями или гос предприятия, собирающие железо на заказ для всяких роскосмосов. Так ли это вообще, или всем похуй/заводи трактор/тащи-код-с-опен-корес-и-не-парься?

если хочешь быть успешным в рашке, то нужно изучать не системверилог, а 1с.

если же настолько упорот, что хочется-таки в электронику, то тут одна лишь надежда на цос. но там годы нужны на погружение в тему.

Не уверен, что в рашке есть конторы, которые пишут на SV.

По поводу работы - ищи на hh и на форуме electronix.ru/forum.

Как ты думаешь, почему именно пользователей линукса называют "красноглазыми", а сам линупс "прыщами"? Ничего не имею против Линукса, просто не люблю, когда обижают винду в тех местах, где и прыщи не блещут

25 Кб, 320x332

25 Кб, 320x332стоит только немного обосрать винду так сразу прибежит какойнибудь спермоглот и начинает кукарекать про линупс, я имел ввиду что ДОС круче винды, при ДОСе такой хуйни с длл небыло

и почему? всегда было интересно это узнать.

Айфон - это кал.

Что делать-то? Если закажу, ждать долго, пока китайцы отдуплятся. Нагуглил что есть какой-то Xilinx Parallel Cable на резисторах и в LPT, как оно ваще, работать будет? Или медленно?

>можно ли заделоть на плисе pll с блекджеком и частотами

А поконкретнее?

В некоторых плисах и встроенные PLL есть.

Плисины там совсем простые, CPLD, а не FPGA. Но примеры годные и их много.

262 Кб, 1227x682

262 Кб, 1227x682вроде бы прошивается, но реконфигурации не происходит. Подключение ног EPCS1 сверил по даташиту и тоже обрывов или других косяков не нашел. В чем может быть проблема?

Только что проверил, сопротивление между TDI и GND - ровно 10кОм. К тому же, даже если б TDI был замкнут на землю, то отдельно прошитый через AS EPCS1 должен был заново сконфигурировать ПЛИС? Или я не прав?

171 Кб, 314x320

171 Кб, 314x320Какого хуя, эта ваша блядская Vivado не поддерживает божественный SystemVerilog? Почему интерфейсы запилены через жопу? Кодогенераторы, враперы, хуяперы! Сколько я еще буду терпеть вот такую хуйню:

.S_AXI_ACLK(s00_axi_aclk),

.S_AXI_ARESETN(s00_axi_aresetn),

.S_AXI_AWADDR(s00_axi_awaddr),

.S_AXI_AWPROT(s00_axi_awprot),

.S_AXI_AWVALID(s00_axi_awvalid),

.S_AXI_AWREADY(s00_axi_awready),

.S_AXI_WDATA(s00_axi_wdata),

.S_AXI_WSTRB(s00_axi_wstrb),

.S_AXI_WVALID(s00_axi_wvalid),

.S_AXI_WREADY(s00_axi_wready),

.S_AXI_BRESP(s00_axi_bresp),

.S_AXI_BVALID(s00_axi_bvalid),

.S_AXI_BREADY(s00_axi_bready),

.S_AXI_ARADDR(s00_axi_araddr),

.S_AXI_ARPROT(s00_axi_arprot),

.S_AXI_ARVALID(s00_axi_arvalid),

.S_AXI_ARREADY(s00_axi_arready),

.S_AXI_RDATA(s00_axi_rdata),

.S_AXI_RRESP(s00_axi_rresp),

.S_AXI_RVALID(s00_axi_rvalid),

.S_AXI_RREADY(s00_axi_rready)

Сколько, я вас спрашиваю? Дали вам SystemVerilog, структуры, интерфейсы и юнионы, нет, блядь, хотим жрать говно, дрочить на текстовые простыни и кодогенерировать. Уебки блядь!

460 Кб, 2304x1728

460 Кб, 2304x1728За Артикс мне поясни, тогда доставлю.

Какую нище-плату выбрать если ты нищестудент и связи с последними событиями в жизни рубля, купить отладочную плату для тебя стало нетривиальной задачей?

Очевидный «Марсоход-2» очевиден. Плюс у стартеркита есть две простенькие платы (одна на Циклоне-4, другая на Спартане-6) с ценой в районе 3 килорублей.

73 Кб, 750x563

73 Кб, 750x563махарайка какая-то. с соседнего треда.

Ты издеваешься, такие пики постить? А на этом у тебя что? Понятно, что отладочная плата. Что в ней за 4 пустых блока? Почему у нее всего 4? Она что, ебанутая?

Эй не кипешуй, это несущая плата для отладки мезонинов. Ты же не дымишь когда видишь, материнскую плату с пустыми PCie слотами

>Какой самый лучший способ для отправки данных с фпга на пекарню?

>SATA2

>USB HS

Разве pcie не легче реализовать?

>SATA

а разве сату получится подключить хост-хост?

она вроде скоростнее сраного усб

а вообще сто мигабит хватит всем по езернету

>В чем соль?

>Просто кристалл с кучей тригерров/счетчиков/таймеров, взаимодействие между которыми мы определяем прошивкой?

Сам спросил - сам ответил.

Ну а что мешает в прости-Господи той же ардунье, там же можно программно делать и таймеры и счетчики и триггеры? Или у неё мала частота опроса входов и выдачи сигналов на выходы?

Вот ты стебаешься, а ПЛИС и вправду другой уровень. Это тебе не для ардуины скрипты писать.

Анчоусы, передо мной стоит задача: сделать устройство, выполняющее некие операции со звуком и делающее из этого картинку. Также имеется дисплей под это дело с параллельным интерфейсом. Так вот, можно ли на плисине сделать помимо обработки аудиосигнала еще рисование картинки в видеопамяти и вывод этой картинки на дисплей? Какое семейство альтеры подойдет? В крайнем случае могу подумать о альтернативах, но альтеровские штуки под рукой.

Один добрый антоним уже освятил меня на использование плис.

> Ну а что мешает в прости-Господи той же ардунье, там же можно программно делать и таймеры и счетчики и триггеры?

Грубо говоря, всё: http://electronics.stackexchange.com/questions/4382/fpgas-vs-microcontrollers

Студентота электронщик, имею относительно хороший опыт в программировании STM. Решил обмазаться ПЛИСами. Так вот с чего начать? С одной стороны есть Марсоход с кучей примеров и статей. Но вот смутило меня то что на ПЛИС которую проект юзает, "всего" 10к логических элементов. Это нормально для начала? ну и еще какие есть отладочные платы с ПЛИСинами которые имеют хорошую учебную базу?

DE2-115 закажи.

Минусы:

-Цена $600

Плюсы:

-115к логических элементов, что очень прилично

-Овердохуя периферии на плате и много светодиодиков с выключательчиками :3

-Есть пдфки с лабами, если не знаешь с чего начать

-Годно выглядит: телки текут, быдло боится

-Для студентов цена всего $300, достаточно прислать скан российского студня.

Алсо сейчас появилась DE1-SoC. Там чуть поменьше логических элементов в плисине и поменьше периферии на борде, но зато есть двухядерный ARM Cortex-A9 прямо в плисине и академ-цена всего 175 бачей.

А вот есть ли какая нибудь хитрая схемка для того что бы можно определить сколько мне логических элементов понадобиться для проектов из определенных областей? Если с МК в моей голове все просто и я могу определить что для этого мне понадобиться приблизительно такой контроллер, то с ПЛИС как то непонятно.

Прикидываешь блок-схему. Ишешь, какими IP-блоками можно её реализовать. Качаешь даташиты на них, там всё расписано по занимаемой логике. Складываешь. У множаешь вполтора раза, а лучше в два, потому что place & route хочет некоторого пространства для действий, чтобы по всем констрейнтам укладываться. Примерно так.

а вот еще один вопрос. Собственно с чего я друг метнулся с МК на ПЛИС. В последнее время меня очень заинтересовало компьютерное зрение, для большинство алгоритмов КЗ на МК жутко тормозят. Более или менее удалось реализовать это контурный анализ на STM32f4 но с хуевым разрешением и само собой о реалтайме речи и не идет. Насколько актуальны реализации алгоритмов КЗ на ПЛИС? есть ли вообще такое? имеет какое нибудь реальное применение? В основном гуглятся какие то абстрактные научные работы не имеющие с сомнительной практической реализуемостью.

Сейчас на opencl под плисы можно писать. Так что, очевидно, что все возможно.

Ты не можешь в ардуине сделать сто счетчиков, работающих параллельно.

>какая нибудь хитрая схемка для того что бы можно определить сколько мне логических элементов понадобиться для проектов из определенных областей?

Пишешь проект, синтезируешь в САПР, оно тебе покажет, сколько чего будет использовано и влезет ли вообще твой проект в выбранный кристалл.

На али всего несколько (это меня смущает больше всего) предложений с 3 speed grade и сотни с 2. Вот, например, http://ru.aliexpress.com/item/Xc6slx9-3tqg144c-xc6slx9-3tqg144-xc6slx9/1039508354.html - реального фото нет, В обязательствах продавца "при несоответсвии товара возврат денег, но пересылка товара за счет покупателя".

Не наебут ли меня, подсунув 2 speed вместо 3?

Вот цитата - Если товар не соответствует описанию, Вы можете вернуть товар, оплатив стоимость обратной пересылки, или оставить товар себе и договориться о компенсации с продавцом

Раньше я встречал только Если товар не соответствует описанию, Вы можете договориться с продавцом о компенсации без необходимости возвращать товар

Хуйня какая-то

>>12737

Это вы про ПЛИС или про что-то конкретное?

так-то и самопрошивка и память в мегабиты на средних ПЛИСах давно есть

За хилых не отвечу точно, а вот как раз про альтеру, если дружишь с верилогом/вхдл, а не с ниосом, то начиная со второго циклона - можно, ну это если есть микросхема цап для VGA или R-2R матрица для того же... с HDMI лично не знаком

Методички - врядли, а вот оупенкорс - в помощь

А что насчет Lattice, посоны? Я смотрел по mouser'у, у них есть сверхдешевые небольшие плиски, самое то для всякого рода несложного dsp для мелкорешений вроде "мк+йобасенсор+плис", нет?

ICE40UL1K-SWG16ITR50

Стоит полтора доллара, on-chip HFS = 48Mhz, в даташите написано, что два вида - 640 и 1000 LUTs.

Ссылочка: http://www.mouser.com/ds/2/225/iCE40UltraLiteDataSheetDS1050-526997.pdf

Для решений мк+сенсор+плис посмотри лучше в сторону Cypress PSoC. У них несколько семейств, особо годные PSoC4 и 5. МК уже внутри, ПЛИСка тоже - небольшая, но для таких применений как предобработка показаний сенсоров обычно хватает. Периодически устраивают распродажи, PSoC4 как-то по доллару раздавали - а там и Cortex M0, и поддержка тач-сенсоров сразу (Cypress сapacitive Sigma-Delta™ (CSD) controller)

>Какие подводные камни?

Никаких /thread Добудь где-нибудь студень, чтобы получить академическую цену.

Это платина. Никак. Плисины предназанчены для программирования булевой логики, и происходит это путем настройки физических связей между компонентами плисины во вземя прошивки. Нейросеть же подразумевает под собой самообучение и создание новых связей в логике. Для данных целей скорее подойдет сигнальник типа тайгер шарк

>>173810

>>178190

Кароч вот для начала по ксайлинксу не было но вот по квартусу альтера http://irs.nntu.ru/students/full_time/bach/210400_62/ смотреть цифровые устройства и микропроцессоры

Даллее для более серьезных дядек непосредственно алгоритмы цос реализуемые на плис (АХТУНГ!!! Много матана и прочего тяжело вопринимаемого мозгом, но точно говорю все рабочее сам почти все реализовывал включая кордик) http://irs.nntu.ru/students/full_time/bach/210400_62/ тут нада смотреть апаратные средства цифровой обработки сигналов и только лекции кафедра намудрила и практика там вобще по сигнальным процам

А если уже обученную нейронную сеть переложить на ПЛИС. И как подступиться к сигнальникам? с ПЛИСами все понятно тысячи плат и сотни материалов. А вот по DSP ничего не видел.

>по DSP ничего не видел

Заходи в наш ламповый ЦОС тред. Алсо, что может быть непонятного в реализации? Складывай, умножай, задерживай. Вот и вся обработка.

Рад тебя видеть друг анон. Без деанона я тоже там был.

>Никак

Ну тащем-та я даже нашел несколько книжек на эту тему, что как бы несколько тебя опровергает. Ссылка в качестве примера: http://lab.fs.uni-lj.si/lasin/wp/IMIT_files/neural/doc/Omondi2006.pdf

>самообучение и создание новых связей в логике

Тоже смутно чувствовал, что это в плисах на данном этапе не реализовать. А если предварительно обучать нейросеть в матлабе (или другом месте), а потом транслировать ее в плис?

Ну значит я ошибался. Честно сказать по нейросетям только базовые знания, я ж не программист, а вот по плисинам много интересного знаю. На том и основывался мой ответ. Но ты попробуй и дерзай

на самом деле при мне как то разбирали какой то еба ПЛАК от Simens, так вот у него как раз процесс управления осуществлялся через нейронную сеть, и там была ПЛИС'ка и весьма внушительных размеров.

Хуй знает сам решай. Звание магистра у меня на работку дает надбавку в 5к в отличие от специалиста, вот и вся разница

нет смысле. Там ПЛИСы ровно один семестр, в конце которого сдаешь небольшой проект - простенький фильтр.

DE0-CV Board

DE0-Nano Development and Education Board

Какой годнее? Первые два на куклоне 5, третий на четвертом.

Первый имеет дохуя памяти котекс9, езернет,отг, микросд,акселерометр,немного кнопочки-лампочки и линупс на борту. Такая малинка с плисиной, но имеет около 12к вентилей.

Второй имеет 50к вентилей, ПС\2 вга на 8резисторах(лол). и 64мбайт срам, микросдшку и тучу кнопочек и лампочек.

Последний имеет акселерометр,слоу ацп, мало кнопочек, немого памяти и даже еепром. Короче всего по немногу, и даже нищебродская цена.22К вентилей.

Я начинающий плисоеб, экс адуринщик. Последняя интересная, но все это есть у моего stmf4discovery. Первая манит своей системой, но видеоядро туда не разместишь, и остается вопрос взаимодействия плисины и линупса в чипе.

Первая вроде норм, теплые семисигментники-кнопочки много вентилей-хватит на многое, но прийдется пердолится с дополнительными микросхемами и канифолить шильдики.

Что из них стоит своих денег?

Предпологается что цена будет студенческая

Подкопи еще 75$ и купи DE1-Soc и там уже все что угодно есть.

Что симулировать?

Кто живые?

Нет, все умерли.

1,9 Мб, 1914x1393

1,9 Мб, 1914x1393Изучаю VHDL.

Так возникает такой вопрос. Переменные вообще имеет смысл использовать внутри блока процессов? Или они только все усложняют и надо стараться обходиться только синхронным и последовательным поведением схемы?

Если кому интересно давайте что ли тут более активный обсуждач с примерчиками разведем.

Вот тебе пример использования переменной:

Допустим, есть сигнал channel(3 downto 0), который где-то как-то щелкает.

Допустим, у тебя есть процесс, в котором, в зависимости от текущего канала, что-то должно происходить. Ты можешь в процессе конструкцию типа

a <= b(conv_integer(channel))

Или же объявить переменную и использовать ее:

current_channel := conv_integer(channel)

a <= b(current_channel)

На первый взгляд, разницы особой нет. Но когда процесс занимает несколько десятков строк, городить везде conv_integer менее удобно.

А, походу дошло, ты имеешь ввиду, что-то навроде этого:

a <= b(conv_integer(channel))

bb <= b(conv_integer(channel))

c <= b(conv_integer(channel))

d <= b(conv_integer(channel))

против этого:

current_channel := conv_integer(channel)

a <= b(current_channel)

bb <= b(current_channel)

c <= b(current_channel)

d <= b(current_channel)

74 Кб, 500x473

74 Кб, 500x473Хз. Как по мне это больше похоже на синтаксический сахар. Если всерьез такое использование рассматривать. Завтра с работы принесу свой модуль в тех вариантах где я логику с помощью переменных реализовывал. Сегодня забыл просто.

В принципе вполне элегантное решение(люблю когда лишних сигналов снаружи не торчит) но вопрос в том насколько корректное. Завтра запощу, если интересно. Можем пообсасывать.

Что значит - насколько корректное?

>больше похоже на синтаксический сахар

Так это и есть синтаксический сахар. VHDL дает тебе инструмент. Пользоваться им или нет - твое дело.

Фишка переменной в том, что в процессе, который тактируется клоком, переменная принимает значение уже на текущем такте. Сигнал же в таком процессе принимает значение только на следующем такте.

177 Кб, 1124x1024

177 Кб, 1124x1024Тебе продают платы дешевле себестоимости, а ты воротишь нос, аки кот с пикчи. Да ты ж охуел!

354 Кб, 1000x1500

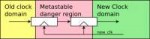

354 Кб, 1000x1500Не это мне понятно. Но зацени процесс.

sync : process (CLK)

variable fd1, fd2 : std_logic := '0';

begin

if (rising_edge(CLK)) then

fd2 := fd1;

fd1 := STROBE;

if (not fd2 and fd1) then

--хитрая колесная логика

end if;

end if;

end process; --sync

Тут CLK - тактовая_лабуда, STROBE - асинхронный гарантировано более длинный чем период нашей частоты сигнал.

Описанный процесс содержит в себе синхронизатора для STROBE и логику которая будет выполняться по его фронту. Более того после небольшой доработки можно сделать что бы по этому фронту выполнялись довольно таки сложные синхронные алгоритмы.

42 Кб, 790x741

42 Кб, 790x741Все отступы упали-пропали .-.

>можно сделать что бы по этому фронту выполнялись довольно таки сложные синхронные алгоритмы

Тактировать что-либо чем-либо кроме чистого клока нельзя, потому что синтезаторы такую времянку рассчитать не могут.

Я неточно выразился. Тактирование осуществляется клоком. А сигнал полученный таким образом можно использовать как сигнал разрешения, например - при взаимодействии с процессором тебе необходимо зафиксировать получаемые от него данные в регистре плис а сделать ты можешь только по приходящим от процессора управляющим сигналам. Протокол EMIF если подробнее. Они для плис вполне себе асинхронные, поэтому их надо синхронизировать и получить из них сигнал разрешения для регистра в котором ты сохраняешь данные.

Ебала какая-то. В любом случае, то что ты описываешь можно описать и без использования переменных.

Раз перекатился, то отвечаю.

>ПЛИС прошивается один раз?

Нет, на ПЛИС есть память, или она загружает конфигурацию с внешней памяти.

>Если была допущена ошибка, то уже не исправить в готовом изделии?

Как ты уже понял, все перепрошивается для большинства микросхем.

>Как экономически вычисляется необходимость реализации проекта в ПЛИС? Чипы же дорогие.

Некоторые вещи нельзя реализовать должным образом на контроллерах, ибо скорости не те+архитектура не тянет задачу оптимальным образом.

>Какие проекты требуют перехода с МК на ПЛИС?

Обработка сигналов, телеком, обработка изображений, высокопроизводительные вычисления, т.е. то, что требует особых архитектурных решений.

Разрываюсь между DE1-Soc и Марсаходом. Поясните какая позиция выгоднее. С одной стороны супер навороченная плата но стоит 250$(студенческая цена + доставка фидексом+ какая то там комиссия) что если учесть курс более чем дахера, НО ее мне хватит наверное до конца жизни по заявленным функциям в изучении.

С другой стороны простенький Марсоход дешевый и зеленый. Сломаю и хуй с ним. Даст возможность попробовать на зубок ПЛИСины. С ним можно будет и SoC посмотреть на сайте есть разобранный подробный проект. Даст ли мне это нормальный скил в плане ПЛИС? И да на Марсоход можно будет прикрутить OpenCL?

http://www.starterkit.ru/html/index.php?name=shop&op=view&id=76

и вот поясните вот за эту платку. Ее можно будет прошить самым дешевым программатором будет с Алиэкспресса или нужно покупать онли почти за 6к?

http://www.starterkit.ru/html/index.php?name=shop&op=view&id=17

в целом могу раскажелиться до 9к, если есть годные варианты буду благодарен.

Насколько я понял из описания, дополнительный программатор не нужен: через ЮСБ ты прошиваешь проц, а потом уже через проц ты заливаешь прошивку в ПЛИС.

Марсоход загугли, лет пять назад помню немного с ним работал - просто, недорого, сайт с примерами хороший.

118 Кб, 680x1024

118 Кб, 680x1024Спасибо, анон

Анон, я правильно понял, CPLD - это один раз зашил в нее логику и оно все? Больше не перебить написанное? А FPGA - забивай новую логику сколько хочешь?

Нужен ПЛИС с паябельным корпусом типа QNF как Lattice XO2.

И сцуко хоть с парой аналоговой периферии вроде компараторов.

Но, видать, не судьба...

*QFN-32

я к тому, что если для тебя QFN-32 паябельный, то с хуев ли остальные корпуса стали непаябельными? явно у тебя станция есть с феном, так не выебывайся жи.

218 Кб, 1920x1080

218 Кб, 1920x1080И самое главное, мне нужны компараторы и операционники. Хотя бы по одному.

это не антенка, хотя, да, разъём SMA. К широкополосному источнику инфракрасного для управления.

25 Кб, 300x280

25 Кб, 300x280В общем, решил я задрачиваться в ПЛИС, есть Altera Max II EPM240T100C5,

Подскажите, какие книги подойдут?

нашел такие:

Стешенко В.Б.ПЛИС фирмы Altera.Проектирование устройств обработки сигналов.2000

Altera - MAX+PLUS II Quartus II (2002)

Поляков_Языки VHDL и VERILOG в проектировании цифровой аппаратуры_2003

Слышал что эта ПЛИС новая, и как бы она новее чем эти все книги, и САПРы которые там описываются, не будет ли проблем? Книг русских вообще мало. А хотелось бы, ну хоть капельку, чтоб въехать. А там уже и по datasheet`ам буду.

двачую

>Слышал что эта ПЛИС новая, и как бы она новее чем эти все книги, и САПРы которые там описываются, не будет ли проблем

Не ссы. Помигай для начала светодиодом. Код (Verilog, VHDL) портируемый на любой (99%) ПЛИС, если не юзаешь локальные фишки. Verlog проще по синтаксису.

Забей на schematics editor сразу. Не труъ.

Чистый верилог без понимания схемы, которая должна получиться в итоге, тоже не тру. Ибо часто у новичков получается обогреватель

В программах под ПЛИСы есть кнопочка, чтобы зазырить, какая схема получилась. Знания цифровой техники никто не отменяет.

И да, на Verilog надо писать аккуратно. Подводные камни описаны в тьюториалах. Verilog =/= C. Не прощает быдлокод.

Ну да, поделишь на ноль - будет КЗ, а там и всю схему пробьёт нахуй.

Внутреннюю логику - довольно сложно

Вот этот парень убил чип, проигнорировав "21000 Combinational loops"

http://www.forrestheller.com/verilog/

в ПЛИС не особо разбираюсь (но, наверное, придется), нужно решение, чтобы подключить большое количество кнопок, которые могут быть нажаты как одновременно, так и по одиночке (пианино), матрицей тут подключить не получится, могу получить ложные срабатывания.

пока этапы такие:

1. Вся логика уже описана на микроконтроллере. (MIDI сигналы)

2. подключил МК по midi к компу.

3. теперь нужны кнопки (размыкатели)

3.1. как лучше реализовать снятия данных о нажатии кнопки, т.е. сигнал с ПЛИС о том что нажато и когда, далее пересылка в МК? реализовать что-то вроде usart? (пока это самое простое на плис) не будет ли это медленно? тут USART, дальше MIDI

3.2. есть ли в ПЛИС возможность сделать триггеры шмитта? или нужно ставить внешние?

первые 2 уже сделал, 3-й в теории, уже разобрался, пока подключил для теста 4 кнопки

какие нахуй ложные срабатывания? даун?

за каким хуем тебе плис? из за портов ввода вывода? обычную матрицу можно просканировать РАСШЫРИТЕЛЕМ портов, можно задрать частоту сканирования до какихнибудь сотен мегагерц и получить норм клавиатуру

или у тебя ардуина? если ардуина то пиздец

6 Кб, 400x387

6 Кб, 400x387>ложные срабатывания?

> матрицу

на картинке нарисовано какие

>ардуина

не ардуина, не AVR, ни PIC.

а даже если и ардуина, это бы вообще не имело значения.

>>191147

> Реакция твоих кнопок?

Т.е.? время реакции? ~5-10мс.

даже если я и использую сдвиговые регистры, мне все равно нужно будет триггеры шмитта, так? итого 17 триггеров шмитта+ 11 сдвиговых регистров. Хочу плис потому что и начусь работать с ней и будет компактней.

>Ложные срабатывания

Ты нарисовал картинку для одновременной работы линий, такого в жизни почти не бывает, тк там идет "развертка" и все твои замыкания засчитываются корректно.

>Триггер

Зачем, боишься дребезга? Программный фильтр?

Вообщем все у тебя упирается в частоту контроллера, которая будет ограничивать скорость реакции нажатия кнопки.

>Ты нарисовал картинку для одновременной работы линий, такого в жизни почти не бывает, тк там идет "развертка" и все твои замыкания засчитываются корректно.

развертка, т.е. "построчное" считывание значений, это как вывод на мониторе, так?

должно срабатывать у меня до 6-8 клавиш одновременно + дублирующие датчики измерения скорости нажатия, итого 12-16 замыкателей, в нажатом состоянии одновременно. При игре дуэтом, допустим, количество нажатых клавиш может увеличиться. ну, скажем плюс 4 клавиши и 4 доп. датчика, соответственно конечно на практике даже по 8 клавиш нажимается редко, но нужно учитывать большой запас

итак, используя матрицу, я смогу добиться выполнения результата поставленной задачи?

справится ли I2C, SPI расширитель портов? http://www.cypress.com/file/37971/download они все сканируют построчно? хотя и ног на МК много

>Зачем, боишься дребезга? Программный фильтр?

пробовал программный фильтр как-то не получилось

1. уход на прерывание

2. отключить прерывания

3. выполнить необходимые действия

4. выдержать время

5. включить прерывания

6. выход из прерывания

где-то происходила запись (скорее всего после ухода на прерывание), о том что прерывание вызвано 2 раза, и дальнейшие действия по программному антидребезгу оказались бессмысленными.

С триггером все чистенько получилось.

>>191348

может ты и прав. но я же ищу решения, рассматриваю варианты, подсчитываю как стоимость так и потраченное время.

Конечно, может идея показаться смехотворной, типа делаешь там себе невротъебенное пианино, с запасом на 4 руки. А сделаешь ли?

Про датчики ты ничего не говорил, что касательно кнопок -- то их ты можешь одновременно хоть сотню зажимать, все упирается лишь в скорость реакции на контакт. Ты хоть схему в протеусе типовую собери, чтобы люди понимали что ты хочешь

датчик - это тоже обычная кнопка, только датчиком будет служить 2 кнопки подключенные к одной клавише. Датчик реализован программным образом - считает время дельта t, чем меньше дельта t, тем, считается, быстрее нажата клавиша.

Ты определись с архитектурой твоей махарайки, а то у тебя кнопка на кнопке кнопкой погоняет и нихуя не понятно как и на чем ты собираешься это вот все реализовывать.

2 Кб, 547x176

2 Кб, 547x176ну смотри,

у меня есть клавиша от клавиатуры пианино, под нее подложено 2 кнопки, пианино должно издать звук только тогда когда обе клавиши нажаты. сттоят они достаточно близко.

как всё происходит: замедленно

1. нажимаем на клавишу форте, сработала кнопка 1, таймер включился - время на таймере пошло.

2. клавиша двигается ниже, включает кнопку 2.

3. кнопка 2 нажата и остановила таймер.

4. происходят вычисления, собранных данных: если ты потихоньку нажимаешь на клавишу, до полного нажатия проходит время 30 мс. - слабое нажатие, звук тише. если скорость нажатия средняя, ну, скажем 20мс, звук погромче. А если пиздунуть по клавише, то инструмент издаст самый громкий звук, т.к. интервал нажатия клавиш самый малый. Имитация молоточковой механики.

5. не дошло дело до второй клавиши, или слишком поздно - таймаут.

Поэтому нужно подключить абсолютно все кнопки, включая всякие там кнопки настроек, уровня звука, переключения инструмента все, что на панели (каждая клавиша включается при одновременном нажатии 2-х кнопок).

только кнопка 1 и 2 будут в обратном порядке нажиматься, ошибся

Тогда тебе по такому вопросу в тред к АРМщикам

не умерай

Ну altpll это же модуль из состава библиотеки квартуса, который инициализирует pll на борту циклона. Так? Можно ли без вызова altpll собственно запусить на нужную мне частоту pll на "чистом" Veriloge? Или только делить стандартные 50 Мгц от кристалла?

Можно, но тебе не понравиться

Попробуй посмотреть на код, который генерит коре генератор. Но ниже инстанса ПЛЛ ты не опустишься, т к. это и есть абстракция хардварного блока на кристале.

Какую ты цель приследуешь?

Да, спасибо, дружище, я в курсе всего этого. Мой странный вопрос был немного о другом. Зачем?

>>195192

Ну вот так вот, захотел освоить мир ПЛИС, а поскольку я программер, решил для себя, что все писать ручками без готовых компонентов, и тут же столкнулся с проблемой, что произвольную частоту кроме как через altpll никак не получить. И либо даже гугл не знает, либо я не знаю как спрашивать у гугла. Максимум что уадлось найти - cycloneive_pll вот здесь https://github.com/rkrajnc/minimig-de1/blob/master/lib/altera/cycloneive_atoms.v - хотя не знаю, оно это или нет. Да и вообще стало интересно, какие есть возможности у разработчика по управлению различными модулями на микросхеме и как это вообще реализовано.

У тебя какой-то странный подход. Ты хочешь всё писать ручками, при этом немножечко далек от внутренней архитектуры устройства, с которым собрался работать.

Во-первых даже pll тебе не даст произвольную частоту, ты подвязан на ту, что есть (в твоем случае 50 МГц), т.е. получить 51.25 МГц тебе будет слегка затруднительно.

Во-вторых, мегафункции там не просто так реализованы. Они позволяют не только быстро реализовать необходимый функционал, но так же сделать это наиболее оптимальным методом.

Всё это развлекалово с клоками в конечном итоге при недостаточной компетенции выльется в ухудшение качества результата твоего труда.

>даже pll тебе не даст произвольную частоту

Ну понятно, очевидно я имел в виду частоту, значение которой отлично от результата деления базовой 50Мгц

>мегафункции там не просто так реализованы

Ок, но это никак не мешает мне сделать свой вариант допустим CORDIC. Да, у него будет меньшая точность и разрадность, но тем не менее для решения задачи - достаточная, и при этом он будет дешевле и быстрей мегафункции.

>в ухудшение качества результата твоего труда.

Это хобби. Я собственно хочу читать данные с АЦП, нужны две частоты 3 и 48 МГц. Как получить нужные частоты через altpll - понятно. Но интерес академический - а можно-ли это сделать без мегафункции?

27 Кб, 549x769

27 Кб, 549x769С Новым Годом типа.

- используете ли make или подобные системы;

- как организовано повторное использование кода;

- есть ли автоматизированная верификация (как юнит-тесты у программистов;

- ну и вообще чем отличается командная разработка на Verilog или VHDL от разработки на C и Java.

Потому что я хорошо представляю, как это делается для больших программных проектов. А вот в Quartus поработал и что-то не вижу, как там скоординировать даже десяток разработчиков.

Интерес вполне праздный.

>вот в Quartus поработал и что-то не вижу, как там скоординировать даже десяток разработчиков

Квартус нужен только чтобы синтезировать проект, а проект должен собираться из исходников. А работа с исходниками может быть организована так же, как и в Си и Джаве - контроль версий, ветки и т.п.

Верификация - с использованием тестбенчей, для SV есть UVM.

>как подбирать "емкость" под желаемый функционал

Эмпирическим путем. Создаешь проект с какой-нибудь ПЛИС, синтезируешь. Если не хватает, берешь ПЛИС пожирнее.

ПС. Нажил кучу epm3032alc44-10n с панельками, хочу на них чего нибудь смастырить. Частотомер например.

Ааа, вона оно как. Спасибо, буду пробовать.

Спасибо. А как именно и чем проект должен собираться из исходников? Вот есть у того же Квартуса инструменты командной строки - надо запускать их из make? А как отслеживать зависимости?

Про тестбенчи и UVM я тоже понимаю. Есть ли практика запускать их автоматически через тот же make? А то в руководствах все больше предлагается смотреть на сигналы глазами.

Это ты CPLD ухватил, притом не самую свежую, бери FPGA - там ячеек на несколько порядков больше.

>>204211

>А то в руководствах все больше предлагается смотреть на сигналы глазами.

А чем на них надо смотреть, анусом?

Или ты предлагаешь программу писать, которая бы определяла правильность диаграмм? А ведь в ней тоже могут быть ошибки, кто их будет проверять, следующий уровень программ? Этак можно до бесконечности.

>>204130

Не могу блядскую ПЛЛку отконфигурировать.

У меня есть входная частота с генератора 16,384МГц, заведённая на одну ногу, мне нужно получить около 50 для ядра и 62,5 для УАРТ-приёмника.

Во-первых: точных частот выставить не удалось; во-вторых: одна ПЛЛка с двух выходов таких частот выдать не может, пришлось ставить две разные, но всё равно довольно грубую точность получил.

Две разные на одну клоковую ногу не ставятся, требует убрать какие-то буферы - я убрал, после чего с горем пополам откомпилировалось. И тут поплыли констрейны: УАРТ-приёмник, тактирующийся 62,5МГц более менее работает, а те схемы которые на 50 - сбоят и что с ними делать не понятно.

Блядский ксилинкс, говно собачье, альтера в 100 раз лучше, глаза бы мои его не видели, камни кривые, софтина кривая, всё криво, всё косо, внутрисхемная отладка через жопу, пиздец нахуй, какие же криворукие мудаки там в разработчиках сидят, охуеть можно.

>А как именно и чем проект должен собираться из исходников?

Не знаю, как там в Квартусе это сделано, в Vivado и PlanAhead есть возможность запуска tcl скриптов. Запускаешь среду, из нее запускаешь скрипт и проект автоматически собирается.

>Есть ли практика запускать их автоматически через тот же make?

Почему бы и нет? Вопрос только в сложности всего этого дела; можно написать скрипт, который будет создавать проект, запускать его на симуляцию и оценивать результаты симуляции, после чего писать результаты в файл.

>программу писать, которая бы определяла правильность диаграмм

Подожди, а зачем в систем-верилоге все эти ассерты, генераторы часов, события, последовательности... Я грешным делом думал, что правильные пацаны выводят из спецификации модуля инварианты, на которые затем пишут ассерты и гоняют тесты, пока не выстрелит. А уж тогда на сигналы смотрят. Не так, значит?

>входная частота с генератора 16,384МГц, нужно получить около 50 для ядра и 62,5

Бро, а на сколько разрядов в делителях PLL ты рассчитываешь? Потому что тебе нужно рациональное приближение для

3.0517578125 = 50/16.384

и 3.8146972656 = 62.5/16.384

Вот нашел тебе калькулятор, рациональное приближение считать: http://www.bee-man.us/math/fraction_approximation.htm

Кварц на 20 МГц не судьба поставить? Было бы все просто.

>Запускаешь среду, из нее запускаешь скрипт

Да tcl скрипт можно и из командной строки запустить, не проблема.

Я-то по привычке считаю, что все, что собирается, должно уметь собираться на билд-сервере, и там же тестироваться. А начальник отдела с утра заглядывает в почтовый ящик и восклицает: "Иванов! Опять в ебутроне регрессия вылезла!"

Вот и пытаюсь понять, насколько это соотносится с обычаями HDL-щиков.

Спасибище!!!!

>>204302

Для начала надо теорию цифровой схемотехники подучить, без неё HDL-языки - как мёртвому припарка.

https://youtu.be/aGMfFezjVnQ

>инварианты

>ассерты

Лол, я таких слов даже не знаю.

>а зачем в систем-верилоге все эти ассерты, генераторы часов, события, последовательности

Если честно, я по систем-верилогу не очень, больше по классическому, как что там не знаю, но думаю, чтобы входные воздействия в тестбенчах было легче создавать. А так чтобы автоматом результаты проверялись - я хз.

Ты мне про рациональные приближения можешь говорить всё что хочешь, но при опорной частоте 16,384МГц на этом сраном спартане 6 с двух разных ПЛЛок я получил 50,79 и 62,256МГц, а на сыклоне 4 я могу получить 49,99 и 62,464МГц из одной ПЛЛки.

Говно без задач этот ваш ксилинкс.

>Кварц на 20 МГц не судьба поставить? Было бы все просто.

Конечно, но плату рисовал не я, приходится работать с тем что есть, будь моя воля я б альтеру поставил.

>мне поставили резистор 100 Ом, а мне нужен 200 Ом. Говно без задач эти ваши резисторы по 100 Ом!

>Говно без задач этот ваш ксилинкс.

Тебе виднее. Уменя крома циклона-2 ничего в хозяйстве нет. Но отношение частот все равно жутко неудобное.

Оказалось достаточно погуглить и почитать форумы вечерок. Поддержка СистемВерилога 2012 есть только в приличных симуляторах вроде Квесты. Ни МоделСим (который идет вместе с Квартусом), ни Вивадо не тянут. А большинство плисанов ими, видимо, и пользуется.

Хуёвенькое твоё сравнение, ибо спартан 6 позиционируется именно как конкурент сыклону 4, на деле же сильно уступает, как минимум по вопросам ПЛЛ, а что будет дальше ещё не известно, я только начал с ним работать.

Есть, посмотри диск идущий с платой Terasic DE2-115, там было, но он, вроде как помню, всё равно на Ниосе крутится.

>спартан 6 позиционируется именно как конкурент сыклону 4, на деле же сильно уступает

>позиционируется

Давай ты еще про говно мамонта вспомнишь? Уже давно вышла седьмая серия, а ты все на Спартане пердолишься.

Я ж тебе говорю, я бы рад не пердолится, но что есть, то есть. Ну так сыклон 5 уже как давно есть.

Тут речь именно спартан 6 vs сыклон 4. Спартан сосёт, хотя вроде бы одного класса.

Квесту можно к чему угодно прикрутить, но ее красть надо, а мне не хочется (да, я странный).

Ладно, попробую, только там все больше по-английски будет.

>я бы рад не пердолится, но что есть, то есть

Ну я и говорю. Ты берешь плату, на которую впаяли резистор 100 Ом и жалуешься, что тебе нужен резистор 200 Ом. При этом мудаками нарекаешь производителей резистора, а не разработчика платы.

Т.е. ты хочешь сказать, что сыклон 4 лучше спартана 6? Ну ок, я тоже к этому склоняюсь.

Я хочу сказать, что плату надо проектировать под свои задачи. А не хуй пойми как.

А нахуя тебе это и что ты хотел закодить?

Бля, доской промахнулся, звиняйте.

Что это такое?

http://marsohod.org/11-blog/265-fpga

Там какие-то схемы и непонятно ничего!

Харрис Д., Харрис С., «Цифровая схемотехника и архитектура компьютера»

http://easyelectronics.ru/files/Book/digital-design-and-computer-architecture-russian-translatino.pdf

Осиливший книгу до конца сможет самостоятельно реализовать процессор на FPGA.

Так Altera или Xilinx?

Достойное упражнение для специальной олимпиады. В целом Альтера поприятней.

Verilog, SystemVerilog, VHDL?

Начни с верилога, а там разберешься.

А где взять?

Плату – купить на http://marsohod.org/ или http://www.aliexpress.com/ (по запросу ''FPGA development board”). Русская версия http://ru.aliexpress.com/, перевод ужасный.

Софт – скачать бесплатно Altera Quartus с http://dl.altera.com/?edition=lite или Xilinx Vivado http://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vivado-design-tools/2015-4.html.

Важно: обе ссылки выше – последние версии продуктов. Они не поддерживают старые чипы. Для них будут нужны http://dl.altera.com/13.0sp1/?edition=web или http://www.xilinx.com/products/design-tools/ise-design-suite/ise-webpack.html.

Так, сразу битая ссылка

Харрис Д., Харрис С., «Цифровая схемотехника и архитектура компьютера»

http://easyelectronics.ru/files/Book/digital-design-and-computer-architecture-russian-translation.pdf

Stephen Brown, Zvonko Vranesic. _Fundamentals of Digital Logic with Verilog Design_

https://www.researchgate.net/file.PostFileLoader.html?id=54d80f66d039b1d37d8b4659&assetKey=AS:273695321329668@1442265458526

Pong P. Chu. _FPGA Prototyping by Verilog Examples_

https://fpga.googlecode.com/files/FPGA Prototyping By Verilog Examples.pdf

Bryan Mealy, Fabrizio Tappero. _Free Range VHDL_

http://freerangefactory.org/pdf/free_range_vhdl.pdf

Peter J. Ashenden. _The Designer's Guide to VHDL, Third Edition_

http://xilinx.eetrend.com/files-eetrend-xilinx/forum/201404/7000-11806-the_designers_guide_to_vhdlpeter_j.ashenden.pdf

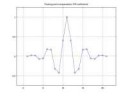

https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/hb/cyclone-iv/cyiv-51005.pdf, страница 5-23. Насколько могу понять, компенсация задержек в сети распределения тактового сигнала.

А схема PLL для IV E там же на рисунке 5-10

Ну по всему выходит, что PLL может синхронизироваться не только внутренней цепью обратной связи через делитель, но и внешней через GCLK например. Нахрена - объяснить не могу, опыта не хватает. Подозреваю, что это как-то компенсирует влияние потребителей на тактовые цепи.

Вот еще про это немного: https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/ug/ug_altpll.pdf

Вот еще пара статей Клиффорда Каммингса - о часах и о сбросах.

http://www.sunburst-design.com/papers/CummingsSNUG2003Boston_Resets.pdf

http://www.sunburst-design.com/papers/CummingsSNUG2008Boston_CDC.pdf

нашел в продаже альтеру, но на 240 вентелей, мне хватит этого для чего-нибудь толкового или стоит копить на вариант поширше?

1,1 Мб, 3870x2958

1,1 Мб, 3870x2958Посмотри на барахолках платы от игровых автоматов, я нажил с десяток нахаляву, сейчас в отпуске соберу программатор и буду тренироваться.

Откуда вы такие лезете с 240 вентилями?

http://ru.aliexpress.com/item/Waveshare-Altera-Cyclone-Board-CoreEP4CE6-EP4CE6E22C8N-EP4CE6-ALTERA-Cyclone-IV-CPLD-FPGA-Development-Core-Board-Full/32433252150.html?spm=2114.03020208.3.114.UQNTon&ws_ab_test=searchweb201556_1,searchweb201644_4_10001_10002_10005_301_10006_10012_10003_10004_62_10007,searchweb201560_8,searchweb1451318400_6149

Кстати она в терре 863р стоит, неужто печатка у косоглазых на целую тыщу тянет?

От 15шт - 528р. Нахуя вот нужны эти китайцы?

57 Кб, 746x626

57 Кб, 746x626Тебе в ёбыч дать, или в глазницы перестанешь долбиться?

Ну там не только печатка, там ещё обвязка, генер, вроде как, тоже денег стоит, монтаж элементов.

Скачай за бесплатно Квартус, спроектируй то, что хочешь и скомпилируй. Сразу увидишь, во что влезет, а во что нет, там можно выбрать целевое устройство.

240 вентилей это маловато, конечно.

Он наверное имел в виду CPLD с 240 макроячейками.

38 Кб, 769x649

38 Кб, 769x649>Как переходить от плавающей точки к целым числам.

Вместо единицы делаешь 1024, вместо 0.5 - 512, вместо 1.5 - 1536. Например.

Ну, во первых, можно все сделать во флоате. Есть для этого все те же корки, ресурсов сожрет немеренно, целесообразность тоже не ясна, но все же. Так, для инфы.

Обычно, 99% случаев, используют fixed point arithmetic. Собственно что на пальцах объяснил >>214877 анон. Тоесть ты не хранишь положение точки в твоем числе, а говоришь. мол точка после третего бита.

У тебя на входе и выходе числа заданной разрядности, поэтому тебе нужна арифметика с фиксированной точкой. Хули непонятного?

>Хули непонятного?

Непонятно зачем мне в каждой арифметической операции учитывать вещественную часть, если мне нужна только целая часть.

лол ты школьнег штоле?

если у тебя есть целые числа, и тебе нужно сделать с ними что то страшное в математическом смысле, то в процессе выполнения математических операций тебе может понадобится увеличить разрядность промежуточных данных (если ты не понимаешь почему то пиздец ), если ты точно уверен что разрядность увеличивать не нужно то нет проблем, если разрядность увеличивать нужно, то есть два стула, увеличивать разрядность целых чисел или не увеличивая разрядность использовать числа с фиксированой запятой с возможной потерей точности, какую стратегию выбрать зависит от требований к проекту а так же от имеющихся ресурсов, в разных варинтах будет разный расход транзисторов против точности, в микроконтролере почти такойже выбор между скоростью, точностью и размером

если ты всего этого незнал т ты явно ардуинщег, хули тебе надо в плисотреде?

Ну ок, теперь более-менее понятно.

>увеличивать разрядность целых чисел

Скорее всего это, так как самих операций немного, большую часть элементов думаю кордик заберет.

Начинает немного прясняться. Например если разрядность значания угла для синуса 32 бита, то для вычисления norm = 2PI/SampleRate, в качестве 2PI необходимо использовать максимальное 32-битное целое число. Верно? И собственно все константы придется вручную вычислять.

И это ковбой, полехче, я конечно не ардуинщик, но всю жизнь писал на СИ, и вот так вот сходу сломать закостенелый мозг и мыслить чистыми битами в отвязке от типов данных не так то и просто. А ПЛИС для меня это хобби.

Ну в принципе да, это наверно перебор, просто для примера. Задача простая, есть сигнал на промежуточной частоте порядка 500кГц-1МГц, оцифровываем с частотой дискретизации порядка 3 МГц, подаем на ПЛИС. ПЛИС выполняет квадратурную демодуляцию, кордик здесь оказался очень удобный, можно сэкономить на множителях, поскольку как я понял, кордик вычисляет как раз I = Xsin(ph), Q = Ycos(ph), где X = Y = семл с АЦП. Если частота дискретизации 3МГц, то да разрадность угла выше 24 бит смысла делать наверно нет.

С большим натягом. Давай проведу маленькую аналогию.

AVR - большой муравей, который и швец и жнец и на дуде игрец - всё умеет, но в каждый момент времени делает что-то одно.

STM32 - муравей пожирнее, всё то же самое, только оче быстро.

ПЛИС - это муравейник. Допустим, что некоторая задача - поле пшеницы. Один муравей может собрать одно зёрнышко за один подход. Тогда соответственно десять муравьёв будут работать в десять раз быстрее. Сто - в сто раз. В зависимости от уровня декомпозиции задачи а плис нужна в параллельных вычислениях чаще всего и количества макроячеек можно построить такой процессор, который будет выполнять поставленную задачу значительно быстрее CPU и даже GPU. Именно поэтому ПЛИС используются в ЦОС - возможность распараллелить вычисления без притаскивания огромной пекарни.

Те же виртексы 7 особенно ультраскейл YOBA-камушки, способные заткнуть за пояс все топовые универсальные процессоры в узких прикладных задачах. Правда в этих задачах почти любая FPGA заткнёт любой процессор.

Флопс это floating point operation.

>Ибо ПЛИСка никаких команд не выполняет.

Но что-то же она выполняет. Тактовая частота есть , регистры есть. Вот например, как в этом хэлоуворде: https://youtu.be/1y-1glsex7c

>Флопс это floating point operation.

Тем более.

>Но что-то же она выполняет.

Она схему твою выполняет. Схема это не программа.

Можно соорудить модуль, который твои плавающие точки вычисляет, а потом этот модуль размножить внутри плис. Любой проц заткнуть за пояс можно, при наличии объёмистой плис.

Ну, к примеру, я хочу сделать свертку изображения (float цвет) 640х480 с фильтром 100х100. Насколько сложна эта задача для плис? Смогёт за один такт?

А если я захочу применить несколько фильтров других размеров, то повторно использовать схему, как я это делаю с кодом процессора, получится?

> Насколько сложна эта задача для плис? Смогёт за один такт?

Зависит от объёма плиски. Большая - сможет.

>А если я захочу применить несколько фильтров других размеров, то повторно использовать схему, как я это делаю с кодом процессора, получится?

Получится после изменений. Как правило, для таких задач пишут программу, которая по исходным требованиям составляет программу в свою очередь для плиски, и уже ещё зашивают в плисину.

При достаточном объёме у тебя в плиске может поместиться даже несколько сверток, которые смогут работать независимо и даже с разной частотой, причём некратной (если предусмотреть тактирование отдельных блоков от своего клока каждый).

> Насколько сложна эта задача для плис? Смогёт за один такт?

>>216614

>Зависит от объёма плиски. Большая - сможет.

В теории - да, на практике - навряд ли.

Если хочешь за один такт, то это должна быть комбинационная схема. Что-то я с трудом представляю, как такой непростой алгоритм можно реализовать на комбинационке.

>>216613

>А если я захочу применить несколько фильтров других размеров, то повторно использовать схему, как я это делаю с кодом процессора, получится?

Если сумеешь создать универсальный модуль, в который твои фильтры передаются из вне - пожалуйста.

Лол, я примерно так же отреагировал, когда мне показали ломалку DES, которой 10 дней на взламывание требуется.

>Хм, звучит круто, даже за 10 тактов она уделает любой проц, кроме дохуяядерных, лол.

Да и двухядерные за 20 тактов.

>А циклон это проц + плис?

Сиклон 5, предыдущие - нет.

>Они могут работать в связке, к примеру проц меняет схему плис в зависимости от задачи?

Точно не скажу.

Плисоводы 80 уровня каким-то макаром могут делать выбор с какой флешки грузить пошивку, тем самым меняя логику в плиске. А в Сыклоне 5 есть проц встроенный, может быть его можно под эту задачу приспособить, я х.з.

>>216798

Логика в плисине на частоте 1,5 Ггц? Что-то ты нам какие-то сказки Андерсона рассказываешь.

>Они могут работать в связке, к примеру проц меняет схему плис в зависимости от задачи?

Так и работают. На проце поднимается линукс, после чего с его помощью можно легко управлять ПЛИС. Например, грузить те же коэффициенты фильтра.

Подскажите ньюфагу, чтобы запилить голосовой УКВ трансивер этого достаточно? Или все же придется паять всякие АЦПы?

1,6 Мб, 1846x1556

1,6 Мб, 1846x1556По возможности накидайте ссылок на тему связи с прабабушкой в Нижневартовске с помощью ПЛИС.

Этого недостаточно.

>ньюфагу

Сразу нет. Порог вхождения весьма высок, а ты, судя по всему, ничего сложнее пердуины в руках не держал, а если и держал, то с аналоговыми ёбушками дел точно не имел, раз не представляешь, как работает трансивер. Конкретно тебе будет дешевле его купить.

Спасибо конечно, учту.

>Конкретно тебе будет дешевле его купить.

Ты что-то перепутал. На кой он мне нужен купленный? Мне и скайпа хватает и нанотехнологий с али. Ну ты понял. А с "аналоговыми ёбушками" разбираться все равно придется.

Видел. И что?

https://marsohod.org/projects/marsohod2/246-fmradio

Вот здесь таки запилили, так что лучше я не буду больше тебя слушать.

Сам то читал что там написано? Это только демонстрация того что возможно сделать такой передатчик (кто бы сомневался).

Но качество сигнала там никакое и будет всюду срать помехами.

Если хочешь сделать приемник подключив антенну напрямую к АЦП, то АЦП потребуется неслабый и еще необходим полосовой фильтр. У наших барыг: https://www.terraelectronica.ru/catalog_info.php?CODE=56414 и то до УКВ не дотянет. И твой циклон-ii тоже не потянет.

Если ты читал внимательно, то там как минимум нужна еще и АНТЕННА в виде куска провода. Поэтому ответ на твой вопрос - "У меня есть циклон, хватит ли этого?" - нет.

Virtex-7 и Virtex-Ultrascale разработчик в треде, задавай свои инпуты

Я серьезно. У меня два 7-х виртекса лежат. Ибо проще каждый год покупать плату, а не лицуху на них, дешевле выходит. Пруфы нужны? Работаю с Kalray, Thales и кучей евроинститутов. Все довольны. 29 лвл

Да, опечатался. Разработчик НА виртексах

Как пришел к успеху в плане работы?

Че пилишь?

Приемник не нужен. Есть rtl свисток. Отлично справляется для начала. Чем сам циклон будет плох как передатчик, если на кварце генерить?

Кусок провода мне достался еще от деда. Он с него на фронте вещал и прикуривал. Должен хорошо работать.

Сама плата физически не может быть АЦП? Хоть с минимальной обвязкой?

С синусом да, но ведь большинству похуй, вещают прямоугольником и счастливы. Кодировки разные есть для цифрового вещания в конце концов. На гармоники и искажения в данном случае похуй, я думаю, не? Уже в зависимости от того, получу ли встроенный АЦП, можно говорить о модуляции.

Что еще за вещание прямоугольником? Насколько знаю, цифра делается путем всевозможных фазовых манипуляций. Или ты не о том?

Насколько я понял, ты хотел сказать что если я не сделаю на выходе модулированный синус, то я ничтожество срущее гармониками во все поля? Вот я и говорю что для начала сойдет и меандр. А про цифровое вещание не узнавал еще, возможно пизданул глупость. Насчет АЦП, щас вот понаходил много статей на тему как реализовать простой АЦП прямо в ПЛИСе. Так что возможно не все так плохо.

Ну можно сделать такой передатчик, можно сделать и приемник (но не на УКВ) на плисине. Но если так не делают, то наверно есть на то причины, не задумывался? А причина проста - никакие характеристики и дорогие комплектующие. Ну сделай, получишь какой-то опыт.

Как ты собираешься реализовывать АЦП прямо на плис? Я смог придумать только как сделать АЦП последовательного приближения. Компаратор есть - LVDS вход. В качестве ЦАП - ШИМ и RC цепочка. Но все равно понадобится минимум один резистор и конденсатор. И частота дискретизации такого АЦП будет хуже некуда.

Посоветовал бы почитать теорию по радиоприему, но, чувствую что бесполезно.

Все что попадалось либо устаревшее, либо вообще не связано с цифрой, либо связано но уже почти не про радио, а про обработку сигналов. Если подскажешь подходящую литературу, буду благодарен!

Получается проблема только в АЦП?

Линейные компоненты на обвязке - это я не считаю чем-то сложным и бессмысленным. А вот добывать и паять отдельные сороконогие микросхемы для преобразователей и фильтров - это как-то западло, тогда вообще непонятно на кой нужны эти ПЛИС, если все равно схема собирается снаружи.

Проблема в твоей голове. Устаревшее у него. Читай литературу, кукаретик, ты очень смешон.

И опять ни названий ни ссылок.

>либо устаревшее, либо вообще не связано с цифрой

У тебя из-за цифры антенна будет по другому работать? Или 2+2 станет равно не 4, а вообще непонятно чему?

Теория полувековой давности вполне применима к "цифровым" радиоприемникам.

Иди, делай уже что-нибудь. Передатчик этот хоть повторил уже?

> вообще непонятно на кой нужны эти ПЛИС, если все равно схема собирается снаружи.

ПЛИС нужна для цифровой обработки сигнала, например для AM\FM демодуляции.

Точнее даже не то что говно. Как-то слабо верится в это.

Правдали что такая очевидная разница? Я как-то романтично думаю, что проблемы вообще нет поменять одно на другое.

Ещё один сравнивальщик тёплого и мягкого.

>Ну там детекторы, фильтры, свертки, цдо.

Ну не знаю в тему мой достаточно абстрактный вопрос или нет. Короче надо на ПЛИС сделать LPF с плавающей частотой среза, и если собственно частота среза изменилась (ну допустим по команде от микроконтроллера), надо перерасчитать матрицу коэффициентов. Но с другой стороны, если уже мы потратили логические элементы на вычисление коэффициентов, то наверно можно вычислять коэффициент в соответсвующей позиции матрицы на каждом такте обработки очередного сэмпла. То есть матрицы фактически не будет, а коэффициент будет вычисляться динамически. Или я сейчас велосипед изобертаю?

>задавай свои ответы.

Используется прямое расширение спектра (DSSS) и код Рида-Соломона. На входе измерено отношение сиигнал/шум, нужно добиться заданной вероятности ошибки на выходе. Какие должны быть параметры у этих двух этапов кодирования для достижения максимальной скорости передачи?

>LPF

low-pass filter?

Если да, то какая реализация? FIR или IIR?

Например это FIR заданного порядка, ну например там 40 или 100. Если у вас будет у такого фильтра меняться частота среза, например вы будете её уменьшать, то будет увеличиваться неравномерность и уменьшаться прямоугольность. Это все будет оказывать как-никак влияние на работу вашей системы.

В такой постановке задачи, я считаю, имеет смысл задаться каким-то приемлимым количеством частот среза и посмотреть их все в матлабе. Ну даже если 100 частот среза, fir фильтр 100 порядка с 32 разрядными коэффициентами. Потратить на это 40кбайт памяти. И по команде загружать нужный набор.

Как ни крути, а память дешевле ресурсы ПЛИС.

Ну может и не том речь.

Кстати а зачем частоту среза-то менять?

Ну... абстракция другая. Тут даже и не програмирование, а схемотехника. Сравнивать и правда не корректно.

Ну если просто сказать, то да. Плис явно сложнее. Уровень вхождения выше, влияние мелочей больше, класс задач решаемых с помощью плис очень сложнее.

+ по статистике алтеры больше 50% проектов на плис содержат процессор. Програмный или аппаратный.

>Есть вариант перескочить на ксайлинкс. Правда говорят там инструментарий говно. На сколько это правда?

После альтеровского Квартуса смотрится убого.

Меня недавно на этот ваш ксилинкс посадили, весь исплевался.

Правда говорят там есть какая-то вивада, как там не знаю, но она только для жирных чипов.

>Pcie между плисами нормальная тема?

А нахуя?

Хуй знает. Я приемники пилю, а не передатчики.

>А нахуя?

ну типа мне надо с одной плис на другую передать 14 Гбит/с + управление на периферию с ответами + прерывания. и у меня как раз есть hard ip pcie 2.0 и 4 трансивера под это дело.

Можно придумать конечно что-нибудь свое. но тут кажется вроде норм решение использовать готовый протокол. хотя он какой-то мутный. Эзернет понятнее был.

>Кстати а зачем частоту среза-то менять?

Ну, я SDR хочу запилить, реализовать на ПЛИС все виды демодуляции, какие смогу осилить. Соответсвенно для каждого вида демодуляции своя ширина канала. Да, наверно сделаю все-же предопределенные таблицы коэффициентов.

>Правда говорят там есть какая-то вивада

Говорят еще она C\C++ транслировать может

>Говорят еще она C\C++ транслировать может

Да может и может, но думается мне хуита в итоге получается.

Может кому-то пригодится

http://ruecm.forum2x2.ru/t52-topic

Сам решил обмазаться Verilog и Xilinx

>для каждого вида демодуляции своя ширина канала.

Тогда разумнее загрузить все таблицы коэффициентов и переключаться между ними

Разумнее запилить канал управления и регистровый интерфейс, а уже через них грузить какие-угодно коэффициенты.

А в этом что-то есть. Я планировал по каналу управления загружать частоту среза, на основании которой генерировались бы коэффициенты. Можно дейстительно и на микроконтроллере генерить и заливать. У меня альтеровский EP4CE10. У него NiosII на борту есть? Может его как раз заиспользовать для этого дела? В смысле для генерации коэффициентов.

Сейчас такой девайс существует, но при малом времени измерения (>100 мс) он безбожно глючит и адски неточен, а нужно иметь точность хотя-бы 0,01Hz

Возникло желание запилить новую версию на ПЛИСине. Так как данных будет слишком много, чтобы запихнуть их в UART, то неплохо бы пихать их в ethernet, для чего понадобится процессор, на который также можно возложить некоторую первичную обработку данных.

Короче присмотрелся к спартан-6 и openRISC.

Буду начинать изучение всей этой лабуды практически с нуля (в универе был курс ознакомления с альтерой на уровне рисования схем из триггеров/счетчиков/регистров), концепцию я представляю, верилог изучу.

Затык ждал в самом начале: где скачать последнюю версию xilinx'овской студии бесплатно без смс?

Сажа прилипла.

Ты бы для начала описал как ты предполагаешь использовать ПЛИС в решении твоей задачи.

Хотел нарисовать блок-схему, но передумал из-за громоздкости.

В любом контроллере уровня STM32 есть несколько аппаратных счетчиков, которые можно настроить на разную херню.

При помощи двух таких счетчиков можно измерять частоту. Один из них просто мотает +1 за каждый такт опорной высокой частоты (считай частоты кварца проца), а другой насчитывает определенное количество импульсов на входе N (измеряемая частота) возможно быстро должен сгенерировать ивент захвата значения счетчика опорной частоты.

В STM32 Я использую ДМА, в камнях поменьше - прерывания.

Затем имея разность двух значений счетчика опорной частоты, а так же зная саму опорную частоту и значение N, можно вычислить саму входящую частоту.

Короче, чем больше опорная частота тем выше точность измерения, а чем меньше время измерения, тем хуже.

Контроллер не подходит по причине отсутствия необходимого количества аппаратных блоков, а вот его производительность полностью устраивает.

Алсо, если сделать все операции по захвату полностью аппаратно, то пропадут редкие выбросы, которые случаются на контроллере из-за наложения прерываний и прочего говна, их сейчас приходится подавлять программно.